东芝采用0.13μm工艺的静电放电(ESD)保护器件适用于模拟功率半导体,可改善静电放电特性

东芝公司(TOKYO:6502)成功研发出一款适用于模拟功率半导体应用的静电放电(ESD)保护器件,产品采用先进的0.13μm工艺技术制造,优化了晶体管结构,显著提高了静电放电特性。静电放电保护鲁棒性提高多达四倍,标准偏差仅为传统结构的十二分之一。三维仿真分析也有助于东芝发现一种机制,优化晶体管结构,提高静电放电鲁棒性。东芝在2016年6月14日于捷克举行的国际半导体研讨会“ISPSD2016”上公布了这些创新成果。

注入来自人体或设备的静电放电浪涌,有可能毁坏半导体器件,因为静电放电电流引起硅材内局部温度上升。需要静电放电保护器件来保护内部电路。这对需要施加10V-100V电压的模拟功率半导体器件来说尤为重要,这些半导体器件需要高额定电压。在这种情况下,静电放电保护器件必须确保大电流,进而导致芯片尺寸增大。缩小静电放电保护器件尺寸成为让芯片更为紧凑的一个课题。

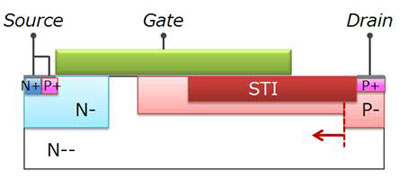

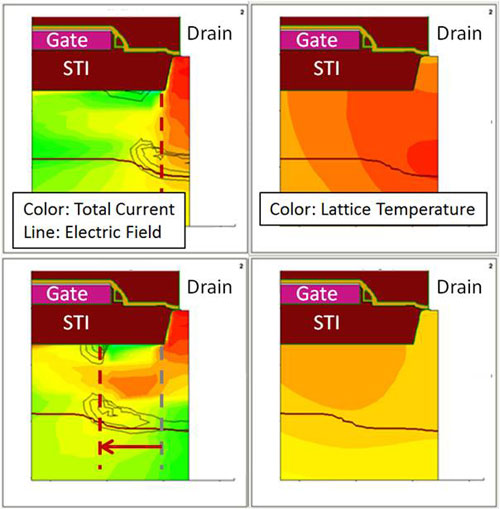

通过静电放电事件三维仿真分析,东芝发现,流经最高电场点的电流导致晶格温度上升,进而导致静电放电诱发的破坏。修改晶体管结构,将漏极低电阻区延伸向源极方向并抑制横向硅电阻,将来自漏极底部的电流转移向源极方向并从最高电场点将其分离。经发现,这一优化设计使静电放电鲁棒性提高多达四倍,而标准偏差减少到十二分之一。此外,该器件确保HBM* ±2000V所需的尺寸减少了68%。

东芝利用0.13μm工艺技术,提供先进的模拟工艺平台,可在该平台嵌入CMOS、DMOS、双极型晶体管等晶体管以及电阻器和电容器等无源器件。用户可从以下三个工艺平台中选择适用于每个应用的工艺:“BiCD-0.13”主要面向汽车(DMOS最高可达100V);“CD-0.13BL”主要面向电机控制驱动器(DMOS最高可达60V)以及“CD-0.13”工艺主要面向电源管理IC (DMOS最高可达40V)。

东芝计划于2017年推出采用CD-0.13工艺技术的产品并继续积极将该工艺技术推广至其他工艺平台,以提高静电放电特性。

* HBM(人体模型):指示静电放电鲁棒性的参数之一

Fig.1 Schematic cross-section of studied structure.

Fig.2 3D-Simulation results for studied structure.

深圳市民森净化科技有限公司,品牌名“JERESD”、“洁迪”,深圳防静电产品厂家是集研发、生产、销售、ESD咨询服务为一体的大型防静电无尘净化类产品、工程技术企业,是"防静电、净化领域"一站式解决方案供应商。专业生产防静电包装袋、工业用椅、防静电手套等静电防护产品。如您对静电防护感兴趣,欢迎洁迪官网咨询在线客服,或致电400-839-1599,我们随时为您服务!

本文出自洁迪资讯http://www.jeresd.com,转载请注明出处!